Publications

Song, B., Michihiro, S., Wang, Z., Masayuki, H., Chattopadhyay, A. and Takashi, S.: A Processor-Level NBTI Mitigation Technique of Applying Anti-Aging Gate Control through Instruction Set Architecture, in In IEICE Conference of VLSI Design Technologies (VLD)(Okinawa Prefecture, Japan), pp. 49-54, IEICE, Mar. 2015

Wang, Z., Chafekar, S., Xie, H., Rama Usha A, S. and Chattopadhyay, A.: Fast, Approximate Error Prediction for Unreliable Embedded Processors, in HiPEAC Workshop on Approximate Computing (WAPCO)(Amsterdam, The Netherlands), pp. 1-6, Jan. 2015

Wang, Z., Xie, H., Chafekar, S., Rama Usha A, S. and Chattopadhyay, A.: Architectural Error Prediction using Probabilistic Error Masking Matrices, in Asia Symposium on Quality Electronic Design (ASQED) (Malaysia), pp. 31 - 36 , 2015, 10.1109/ACQED.2015.7274003 ©2015 IEEE

Wang, Z.: High-level Modeling, Estimation and Exploration of Reliability for MPSoC, 2015, 10.1109/IWCIT.2015.7140217

Wang, Z., Yang, L. and Chattopadhyay, A.: Architectural Reliability Estimation using Design Diversity, in International Symposium on Quality Electronic Design (ISQED)(San Jose, USA), pp. 112 - 117 , 2015, ISBN: 978-1-47997-580-8, 10.1109/ISQED.2015.7085409

Wang, Z., Paul, G. and Chattopadhyay, A.: Processor Design with Asymmetric Reliability, in IEEE Computer Society Annual Symposium on VLSI (ISVLSI)(Tampa, Florida, USA), pp. 565 - 570 , Jul. 2014, 10.1109/ISVLSI.2014.63 ©2014 IEEE

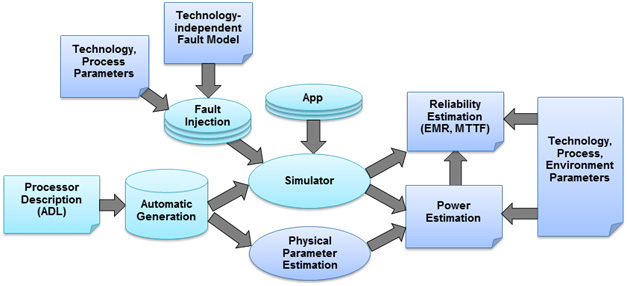

Wang, Z., Chen, C., Sharma, P. and Chattopadhyay, A.: System-level Reliability Exploration Framework for Heterogeneous MPSoC, in ACM Great Lakes Symposium on VLSI (GLSVLSI)(Houston, USA), pp. 9--14, ACM, May. 2014, ISBN: 978-1-45032-816-6, 10.1145/2591513.2591519 ©2014 IEEE

Wang, Z., Li, R. and Chattopadhyay, A.: Opportunistic Redundancy for Improving Reliability of Embedded Processors, in 8th IEEE International Design & Test Symposium (IDT)(Marrakesh, Morocco), pp. 1-6, Dec. 2013, 10.1109/IDT.2013.6727090

Wang, Z., Wang, L., Xie, H. and Chattopadhyay, A.: Power Modeling and Estimation during ADL-driven Embedded Processor Design, in 4th International Conference on Energy Aware Computing Systems & Applications (ICEAC)(Istanbul, Turkey), 2013, ISBN: 978-1-47992-543-8

Wang, Z., Singh, K., Chen, C. and Chattopadhyay, A.: Accurate and Efficient Reliability Estimation Techniques during ADL-Driven Embedded Processor Design, in Design Automation and Test in Europe (DATE)(Grenoble, France), pp. 547--552, EDA Consortium, 2013, ISBN: 978-1-45032-153-2 ©2013 IEEE

Wang, Z., Chen, C. and Chattopadhyay, A.: Fast Reliability Exploration for Embedded Processors via High-level Fault Injection, in International Symposium on Quality Electronic Design (ISQED)(San Jose, CA, USA), pp. 265-272, 2013, ISBN: 978-1-46734-951-2, 10.1109/ISQED.2013.6523621

Kammler, D., Guan, J., Ascheid, G., Leupers, R. and Meyr, H.: A fast and flexible Platform for Fault Injection and Evaluation in Verilog-based Simulations, in Proceedings of the IEEE International Conference on Secure Software Integration and Reliability Improvement (SSIRI)(Shanghai, China), pp. 309--314, Jul. 2009