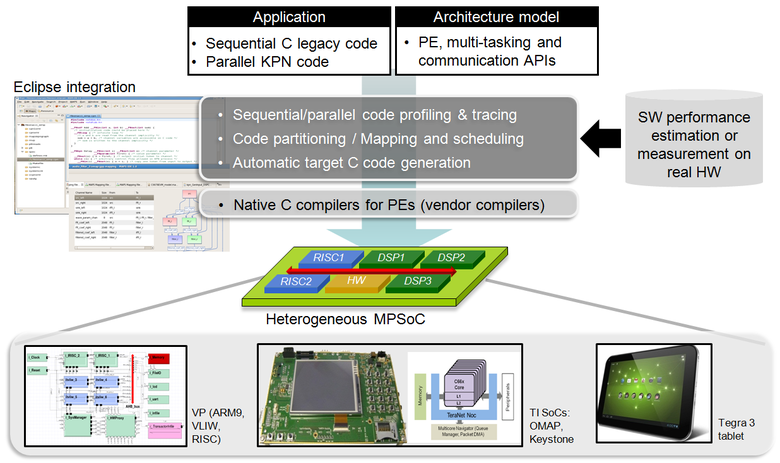

Leupers, R., Aguilar, M. A., Eusse, J. F., Castrillon, J. and Sheng, W.: MAPS: A Software Development Environment for Embedded Multicore Applications, in Handbook of Hardware/Software Codesign,Dordrecht, Sep. 2017

Aguilar, M. A., Leupers, R., Ascheid, G., Kavvadias, N. and Fitzpatrick, L.: Schedule-Aware Loop Parallelization for Embedded MPSoCs by Exploiting Parallel Slack, in 20th Design Automation and Test in Europe Conference (DATE)(Lausanne, Switzerland), pp. 1237-1240 , European Design and Automation Association, Mar. 2017, 10.23919/DATE.2017.7927178 ©2017 IEEE

Aguilar, M. A. and Leupers, R.: Towards Effective Parallelization and Accelerator Offloading for Heterogeneous Multicore Embedded Systems, in Proceedings of the Twelfth International Summer School on Advanced Computer Architecture and Compilation for High-Performance and Embedded Systems (ACACES), HiPEAC, Jul. 2016

Aguilar, M. A., Leupers, R., Ascheid, G. and Murillo, L. G.: Automatic Parallelization and Accelerator Offloading for Embedded Applications on Heterogeneous MPSoCs, in 53rd Design Automation Conference (DAC)(Austin, TX, USA), Jun. 2016, ISBN: 978-1-45034-236-0, 10.1145/2897937.2897991

Leupers, R., Schürmans, S., Aguilar, M. A. and Führ (Onnebrink), G.: Power-Aware Multicore Software Development, in Embedded World Conference 2016, Feb. 2016

Aguilar, M. A. and Leupers, R.: Unified Identification of Multiple Forms of Parallelism in Embedded Applications, in ACM SRC at 24th International Conference on Parallel Architectures and Compilation Techniques (PACT), Oct. 2015

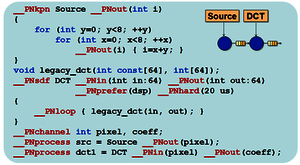

Aguilar, M. A., Eusse, J. F., Leupers, R., Ascheid, G. and Odendahl, M.: Extraction of Kahn Process Networks from While Loops in Embedded Software, in 12th IEEE International Conference on Embedded Software and Systems (ICESS), pp. 1078-1085, Aug. 2015, 10.1109/HPCC-CSS-ICESS.2015.158 ©2015 IEEE

Aguilar, M. A., Eusse, J. F., Ray, P., Leupers, R., Ascheid, G., Sheng, W. and Sharma, P.: Parallelism Extraction in Embedded Software for Android Devices, in Proceedings of the XV International Conference on Embedded Computer Systems: Architectures, Modeling and Simulation (SAMOS), Jul. 2015, 10.1109/SAMOS.2015.7363654 ©2015 IEEE

Aguilar, M. A., Leupers, R., Ascheid, G. and Kavvadias, N.: A Toolflow for Parallelization of Embedded Software in Multicore DSP Platforms, in Proceedings of the 18th International Workshop on Software and Compilers for Embedded Systems (SCOPES)(New York, NY, USA), pp. 76--79, ACM, Jun. 2015, ISBN: 978-1-45033-593-5, 10.1145/2764967.2771936

Aguilar, M. A., Jimenez, R., Leupers, R. and Ascheid, G.: Improving Performance and Productivity for Software Development on TI Multicore DSP Platforms, in Proceedings of the 6th European Embedded Design in Education and Research Conference (EDERC), pp. 31 - 35, Sep. 2014, 10.1109/EDERC.2014.6924353 ©2014 IEEE

Odendahl, M., Castrillon, J., Volevach, V., Leupers, R. and Ascheid, G.: Split-Cost Communication Model for Improved MPSoC Application Mapping, in Proceedings of the International Symposium on System-on-Chip (SoC), Oct. 2013, 10.1109/ISSoC.2013.6675280 ©2013 IEEE

Sheng, W., Schürmans, S., Odendahl, M., Leupers, R. and Ascheid, G.: Automatic Calibration of Streaming Applications for Software Mapping Exploration, in Design & Test, IEEE, Vol. 30, No. 3, pp. 49-58 , Mar. 2013, ISSN: 2168-2356, 10.1109/MDT.2012.2204852 ©2013 IEEE

Sheng, W., Schürmans, S., Odendahl, M., Bertsch, M., Volevach, V., Leupers, R. and Ascheid, G.: A Compiler Infrastructure for Embedded Heterogeneous MPSoCs , in 2013 International Workshop on Programming Models and Applications for Multicores and Manycores (PMAM 2013)(New York, NY, USA), pp. 1-10, ACM, Feb. 2013, ISBN: 978-1-45031-908-9, 10.1145/2442992.2442993

Sheng, W., Wiebe, A., Stulova, A., Leupers, R., Kienhuis, B., Walters, J. and Ascheid, G.: FIFO Exploration in Mapping Streaming Applications onto the TI OMAP3530 Platform: Case Study and Optimizations, in IEEE 6th International Symposium on Embedded Multicore SoCs (MCSoC-12), Sep. 2012 ©2012 IEEE

Odendahl, M., Sheng, W., Aguilar, M. A., Leupers, R. and Ascheid, G.: Automated Code Generation of Streaming Applications for C6000 Multicore DSPs, in 5th European DSP Education and Research Conference, Sep. 2012 ©2012 IEEE

Stulova, A., Leupers, R. and Ascheid, G.: Throughput Driven Transformations of Synchronous Data Flows for Mapping to Heterogeneous MPSoCs, in SAMOS XII: International Conference on Embedded Computer Systems: Architectures, Modeling and Simulation, Jul. 2012, ISBN: 978-1-46732-296-6 ©2012 IEEE

Castrillon, J., Schürmans, S., Stulova, A., Sheng, W., Kempf, T., Ishaque, A., Leupers, R., Ascheid, G. and Meyr, H.: Component-based Waveform Development: the Nucleus Tool Flow for Efficient and Portable SDR, in Proceedings of the SDR'10 Technical Conference and Product Exposition(Washington D.C., USA), pp. 476--481, Dec. 2010

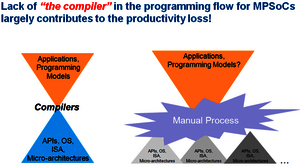

Leupers, R., Thiele, L., Nie, X., Kienhuis, B., Weiss, M. and Isshiki, T.: Cool MPSoC Programming, in Proc. of the Design, Automation and Test in Europe Conference (DATE 2010)( Dresden, Germany), pp. 1488-1493, EDAA, Mar. 2010, ISBN: 978-3-98108-016-2

Castrillon, J., Velasquez, R., Stulova, A., Sheng, W., Ceng, J., Leupers, R., Ascheid, G. and Meyr, H.: Trace-based KPN Composability Analysis for Mapping Simultaneous Applications to MPSoC Platforms, in Proceedings of the Conference on Design, Automation and Test in Europe (DATE '10)(Dresden, Germany), pp. 753--758, Mar. 2010, ISBN: 978-3-98108-016-2

Leupers, R. and Castrillon, J.: MPSoC Programming using the MAPS Compiler, in Proceedings of the 15th Asia and South Pacific Design Automation Conference (ASP-DAC '10)(Taipei, Taiwan), pp. 897--902, Jan. 2010, ISBN: 978-1-42445-766-3 ©2010 IEEE

Leupers, R., Sheng, W. and Castrillon, J.: Software Compilation Techniques for MPSoCs , , No. 10.1007/978-1-4419-6345-1_23p.p.639--678,Heidelberg, 2010, ISBN: 978-1-44196-344-4

Ramakrishnan, V., Adrat, M., Kempf, T., Castrillon, J., Ascheid, G., Leupers, R., Meyr, H. and Antweiler, M.: SDR Waveform Development: Towards Tool Assisted Mapping and Evaluation in the Nucleus Concept, in Proceedings of the SDR'09 Technical Conference and Product Exposition(Washington D.C., USA), pp. 1-18, Dec. 2009

Castrillon, J., Zhang, D., Kempf, T., Vanthournout, B., Leupers, R. and Ascheid, G.: Task Management in MPSoCs: an ASIP Approach, in Proceedings of the 2009 IEEE/ACM International Conference on Computer-Aided Design (ICCAD '09)(San Jose, California, USA), pp. 587--594, Nov. 2009, ISBN: 978-1-60558-800-1

Ceng, J., Sheng, W., Castrillon, J., Stulova, A., Leupers, R., Ascheid, G. and Meyr, H.: A High-Level Virtual Platform for Early MPSoC Software Development, in International Conference on Hardware/Software Codesign and System Synthesis (CODES-ISSS 2009)(Grenoble, France), pp. 11--20, Oct. 2009, ISBN: 978-1-60558-628-1

Leupers, R., Vajda, A., Bekooij, M., Ha , S., Doemer, R. and Nohl, A.: Programming MPSoC platforms: Road works ahead!, in Proc. of the Design, Automation and Test in Europe Conference and Exhibition (DATE 2009)(Nice, France), pp. pp. 1584-1589, Apr. 2009, 10.1109/DATE.2009.5090917 ©2009 IEEE

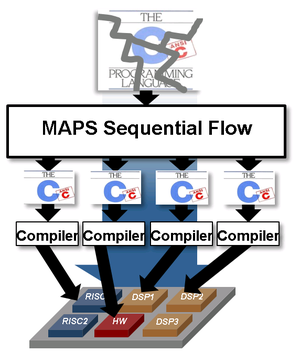

Ceng, J., Castrillon, J., Sheng, W., Scharwächter, H., Leupers, R., Ascheid, G., Meyr, H., Isshiki, T. and Kunieda, H.: MAPS: An Integrated Framework for MPSoC Application Parallelization, in 45th Design Automation Conference (DAC '08)(Anaheim, CA, USA), pp. 754--759, ACM, Jun. 2008, ISBN: 978-1-60558-115-6